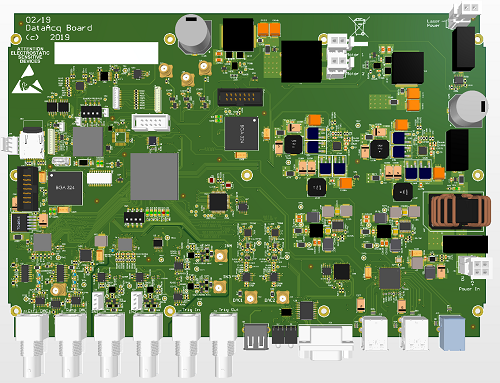

Multi Channel Data Acquisition And Processing System

|

Utilising powerful floating-point Sharc DSPs from Analog Devices and an Altera Cyclone FPGA, this data acquisition system generates stimulation waveforms and then captures and processes multiple input signals in hardware and firmware on board before transmitting raw and processed signals to the PC and output DACs. Raw signal traces are pre-processed by the FPGA to validate the data and pick out the portion of the data to process by the DSPs. The DSPs are then fed the relevant subset of the raw data to then perform more intensive but precise processing of the captured signal. This can be performed up to 10k times a second subject to capture configuration. The multiple processing algorithms within the DSP yeild a number of processed outputs which are presented to the user via a set of analogue voltage outputs through the front panel BNC connectors. Configuration provided by the host / micro-controller allow the user to select which parameter they wish to measure from each BNC output. Scheduled triggering and clocking is carried out the FPGA, ensuring that the system remains synchronous and locked between channels along with driving a dual high speed DAC allowing arbitrary waveforms to stimulate the system under test as appropriate. Providing system housekeeping is an NXP ARM 7 micro-controller. Via a dedicated USB connection to a host computer, the micro-controller handles all on-board storage of calibration data and firmware for both the DSPs and FPGA along with performing scheduled monitoring tasks and event logging to SD card storage. The entire card operates from a single +24V supply consuming under 15watts of power when running but also provides power outputs for other parts of the system that can be controlled by the host PC. |

|

|

|